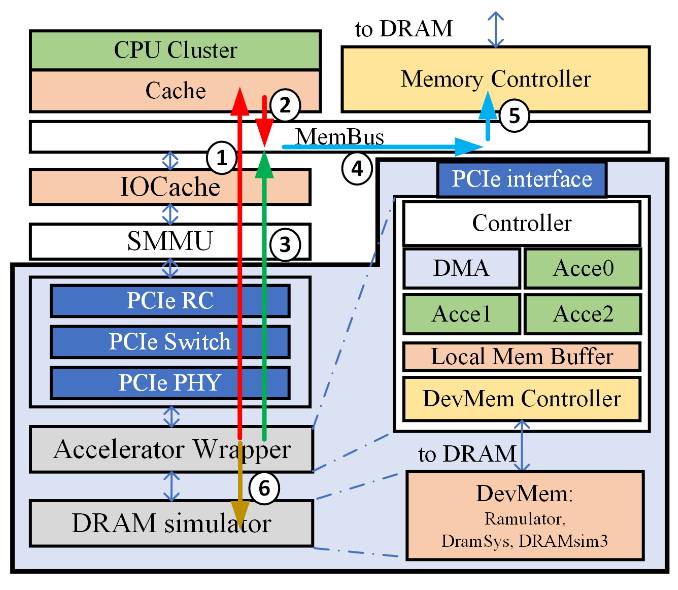

One of our teams has rolled out Gem5-AcceSys: an innovative framework for a system-level exploration of standard interconnects and configurable memory hierarchies.

A series of tests using this new technology will be presented at the Design Automation Conference in San Francisco.

In this study it has been shown that optimized interconnects can achieve up to 80% of device-side memory performance and, in some scenarios, even surpass it. Exciting results for system architects, offering a balanced approach to performance and cost in next-generation accelerator design.

Congratulations to Qunyou Liu, Marina Zapater and David Atienza for this excellent work!

Gem5-AcceSys: Enabling System-Level Exploration of Standard Interconnects for Novel Accelerators

Liu, Qunyou; Zapater, Marina; Atienza, David